- 您现在的位置:买卖IC网 > Sheet目录3881 > PIC18F4539T-E/ML (Microchip Technology)IC PIC MCU FLASH 12KX16 44QFN

2002 Microchip Technology Inc.

Preliminary

DS30485A-page 223

PIC18FXX39

BRA

Unconditional Branch

Syntax:

[ label ] BRA n

Operands:

-1024

≤ n ≤ 1023

Operation:

(PC) + 2 + 2n

→ PC

Status Affected:

None

Encoding:

1101

0nnn

nnnn

Description:

Add the 2’s complement number

‘2n’ to the PC. Since the PC will

have incremented to fetch the next

instruction, the new address will be

PC+2+2n. This instruction is a

two-cycle instruction.

Words:

1

Cycles:

2

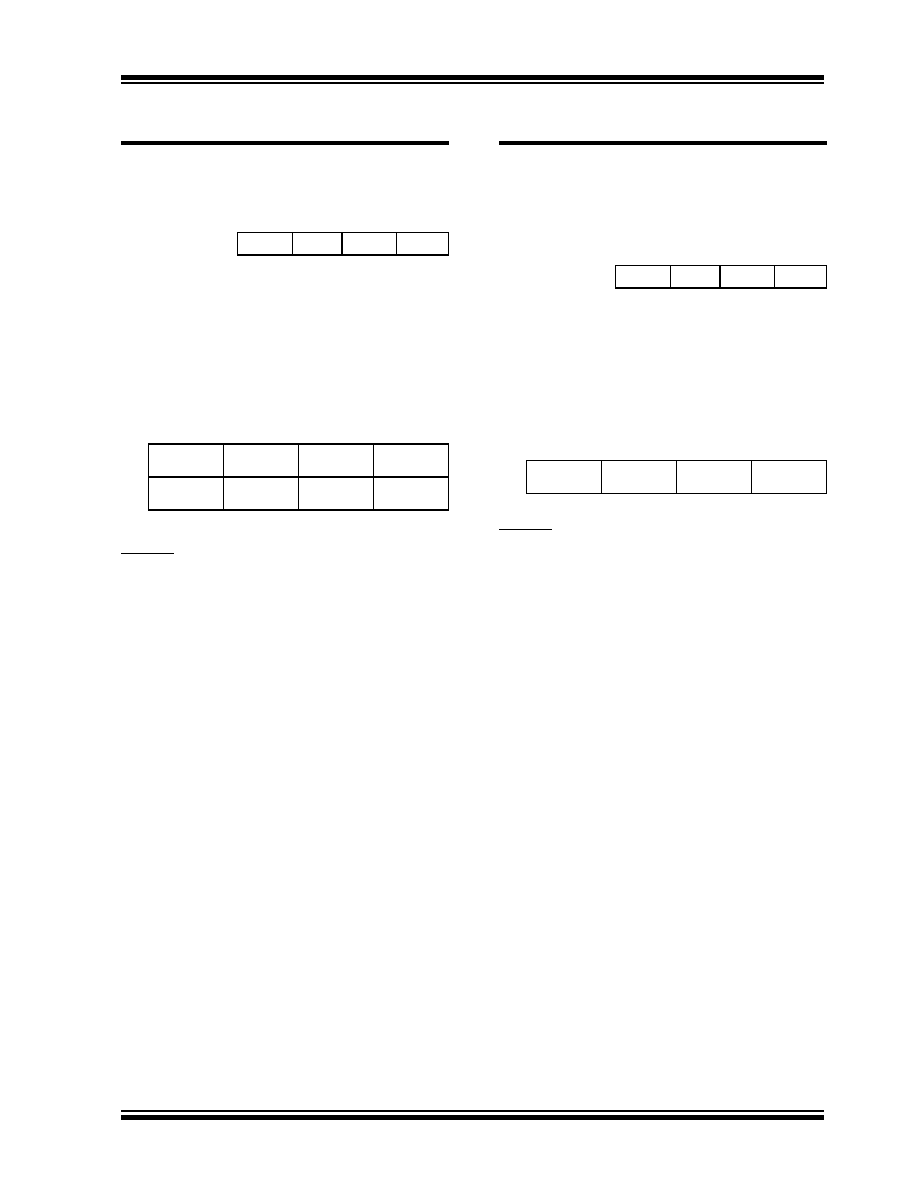

Q Cycle Activity:

Q1

Q2

Q3

Q4

Decode

Read literal

'n'

Process

Data

Write to PC

No

operation

No

operation

No

operation

No

operation

Example:

HERE

BRA

Jump

Before Instruction

PC

=

address (HERE)

After Instruction

PC

=

address (Jump)

BSF

Bit Set f

Syntax:

[ label ] BSF f,b[,a]

Operands:

0

≤ f ≤ 255

0

≤ b ≤ 7

a

∈ [0,1]

Operation:

1

→ f<b>

Status Affected:

None

Encoding:

1000

bbba

ffff

Description:

Bit 'b' in register 'f' is set. If ‘a’ is 0

Access Bank will be selected, over-

riding the BSR value. If ‘a’ = 1, then

the bank will be selected as per the

BSR value.

Words:

1

Cycles:

1

Q Cycle Activity:

Q1

Q2

Q3

Q4

Decode

Read

register 'f'

Process

Data

Write

register 'f'

Example:

BSF

FLAG_REG, 7, 1

Before Instruction

FLAG_REG

=

0x0A

After Instruction

FLAG_REG

=

0x8A

发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

PIC18LF8680T-I/PT

IC PIC MCU FLASH 32KX16 80TQFP

PIC16F1936-I/SO

IC PIC MCU FLASH 512KX14 28-SOIC

PIC18F24K20-I/SO

IC PIC MCU FLASH 8KX16 28SOIC

PIC18LF8585T-I/PT

IC PIC MCU FLASH 24KX16 80TQFP

XF2J-3024-11

CONN FPC 30POS 0.5MM SMT

PIC18LF6525T-I/PT

IC PIC MCU FLASH 24KX16 64TQFP

PIC18LF8621T-I/PT

IC PIC MCU FLASH 32KX16 80TQFP

PIC18F8620T-E/PT

IC PIC MCU FLASH 32KX16 80TQFP

相关代理商/技术参数

PIC18F4539T-E/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539T-I/ML

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4539T-I/PT

功能描述:8位微控制器 -MCU 24KB 1408 RAM 32 I/O RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550EPT

制造商:Microchip Technology Inc 功能描述:

PIC18F4550-I/ML

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550-I/P

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550-I/PT

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT

PIC18F4550T-I/ML

功能描述:8位微控制器 -MCU 32kBF 2048RM FSUSB2 RoHS:否 制造商:Silicon Labs 核心:8051 处理器系列:C8051F39x 数据总线宽度:8 bit 最大时钟频率:50 MHz 程序存储器大小:16 KB 数据 RAM 大小:1 KB 片上 ADC:Yes 工作电源电压:1.8 V to 3.6 V 工作温度范围:- 40 C to + 105 C 封装 / 箱体:QFN-20 安装风格:SMD/SMT